* 참고 교재

컴퓨터 시스템 구조론 - 예스24 (yes24.com)

컴퓨터 시스템 구조론 - 예스24

컴퓨터 시스템 구조론

www.yes24.com

* 반도체 주기억장치

반도체 기억 소자

반도 기억장치의 기본 요소는 기억 소자(memory cell)이다.

반도체 기억 소자의 성질은 아래와 같다.

- 2개의 안정된(혹은 반안정된) 상태인 2진수 1 또는 0을 갖는다.

- 상태를 세트(set)할 수 있도록 적어도 한 번은 쓰여질 수 있다.

- 상태를 감지할 수 있도록 읽혀질 수 있다.

반도체 기억 소자의 동작

Select(선택 단자): 읽기 또는 쓰기 동작을 할 기억 소자를 선택한다.

Control(제어 단자): 수행할 동작이 읽기인지 쓰기인지 지정한다.

Data in: 쓰기 동작인 경우 기억 소자의 상태를 1 또는 0으로 세트 할 전기 신호가 들어오는 통로가 된다.

Sense: 읽기 동작인 경우 소자의 상태를 출력하는 데 사용된다.

RAM(Random Access Memory: 임의 액세스 기억장치)

- 기억장치의 각 단어(word)들은 선으로 연결된 주소지정 회로를 통해 직접 액세스 된다.

- 데이터 읽기/쓰기가 가능하다.

- 일시적 저장장치이다. 즉, 휘발성(volatile)이기에 전원 공급이 필요하다.

- 제조 기술에 따라 DRAM과 SRAM으로 분류된다.

DRAM(Dynamic RAM: 동적 RAM)

DRAM은 커패시터에 전하를 충전하는 방식으로 데이터를 저장하는 기억 소자(memory cell)들로 구성되어 있다.

커패시터는 방전하는 성질이 있기 때문에 전력이 공급되어도 데이터의 저장 상태를 유지하기 위해 주기적으로 재충전해야 한다.

→ Dynamic은 전하가 누설(leak away)되는 성질을 의미한다.

커패시터는 일정 범위 내의 어떤 전하값도 저장이 가능하기에 아날로그 장치이며,

가격이 저렴하고 대용량 기억장치를 구성할 수 있다.

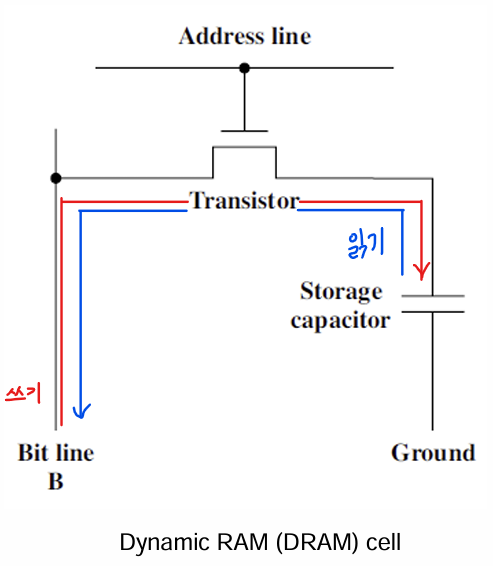

DRAM 소자

주소 선(Address line)은 동적 소자로부터 비트 값이 읽혀지거나 쓰여질 때 활성화된다.

트랜지스터(Transistor)는 전압이 주소선에 가해지면 닫히고(전류 흐름), 전압이 가해지지 않으면 열리는(전류 흐르지 못함) 스위치로 동작한다.

쓰기 동작

1. 전압이 비트 선(Bit line)에 가해진다.(높은 전압은 1, 낮은 전압은 0)

2. 주소 선으로 신호가 들어오며 전하가 커패시터로 전송된다.

읽기 동작

1. 주소 선이 선택되면 트랜지스터가 켜진다.

2. 커패시터에 저장된 저하가 비트 라인을 통해 나와서 감지 증폭기(sense amplifier)로 보내진다.

3. 감지 증폭기는 기준 전압과 커패시터 전압을 비교하여 소자가 가진 값이 1인지 0인지 결정한다.

4. 읽기 동작을 하면 커패시터가 방전되기 때문에 전하를 복원해야 동작이 완료된다.

SRAM(Static RAM: 정적 RAM)

- SRAM은 filp-flop 논리 게이트를 이용하여 저장하는 디지털 장치이다.

- 전력이 공급되는 동안에는 데이터를 계속 유지하기 때문에 재충전이 필요하지 않다.

- DRAM에 비해 크기가 크고 복잡하며, 캐시 기억장치로 사용된다.

SRAM 소자

4개의 트랜지스터(T1, T2, T3, T4)가 안정된 노리 상태를 발생할 수 있는 배열로 서로 연결되어 있다.

논리적 상태 1: 점 C1은 높고 C2는 낮다. T1과 T4는 Off, T2와 T3은 ON 상태이다.

논리적 상태 0: 점 C1은 낮고 C2는 높다. T1과 T4는 On, T2와 T3은 Off 상태이다.

주소 선은 2개의 트랜지스터(T5, T6)를 제어한다. 2개의 트랜지스터가 ON 되면 쓰기 또는 읽기 동작을 수행한다.

쓰기 동작: 원하는 비트 값이 선 B로 들어온다.

읽기 동작: 비트 값이 선 B로부터 읽혀진다.

DRAM vs SRAM

DRAM과 SRAM은 모두 휘발성이기에 비트 값을 유지하기 위해 기억 소자로 전력이 계속 공급되어야 한다.

| DRAM | SRAM |

| 더 간단하고 작다. | 복잡하고 크다. |

| 밀도가 더 높다. (단위 면적 당 소자수가 많다. ) | 밀도가 낮다. |

| 더 싸다. | 더 비싸다. |

| 재충전 회로가 필요하다. | 재중천이 필요하지 않다. |

| 더 느리다. | 더 빠르다. |

| 대용량 기억장치에 주로 사용된다. | 캐시 기억장치로 사용된다. |

ROM(Read Only Memory: 읽기 전용 기억장치)

- 비휘발성이기에 전원 장치가 불필요하다.

- ROM의 내용을 읽기는 가능하지만 ROM에 쓰기는 불가능하다.

- 빈번히 사용되는 라이브러리 서브루틴, 시스템 프로그램, 함수표에 활용된다.

- 데이터를 삽입하는 과정에서 비교적 높은 고정 비용이 든다.

- 하나의 비트라도 잘못되면 모든 ROM을 버려야 한다.

PROM(Programmable ROM)

- 사용자가 임의로 데이터를 1번 쓸 수 있다.(특수 장치 필요)

- 특정 내용을 저장할 ROM의 수가 적을 때 가격이 저렴해 유용하다.

EPROM(Erasable PROM: 삭제 가능한 PROM)

- 자외선을 이용하여 모든 소자를 초기화시킨다.(약 20분 소요)

- 여러 번 지우고 쓰는 것이 가능하지만 PROM보다 비싸다.

EEPROM(Electrically EPROM: 전기적으로 삭제 가능한 PROM)

- 쓰기 전에 그 전의 내용을 지울 필요 없다.

- 버스 제어, 주소 및 데이터 선을 이용하여 주소 지정된 한 바이트 또는 몇 바이트만 갱신할 수 있다.

- EPROM보다 밀도가 낮으며 비싸다.

플래시 메모리

- 기억 소자의 한 영역(블록 단위)이 단 한 동작만에 삭제 가능하다.(바이트 단위 삭제 불가)

- EPROM보다 훨씬 빠르다.

칩 논리

반도체 기억장치는 패키지 된 칩으로 출고된다. 각 칩은 기억 소자 배열을 포함하고 있다.

기억 소자의 배열은 B개의 비트들로 이루어진 W개의 단어로 구성되어 있다.

또한 정방형 배열 구조를 사용하며, 용량이 매 세대 당 4배씩 증가한다.(주소핀 1개 추가: 행/열 2배 증가))

16Mbit DRAM은 4비트로 이루어진 4M(2^22)개의 단어로 구성되어 있다.

기억장치 배열은 2048x2048개의 정방형 소자 배열이며, 2048개의 행들 중 하나를 선택하기 위해 11개의 주소선들이 필요하다.(2^11 = 2048)

4M을 표현하기 위해 필요한 주소 비트 수는 22(2^22)인데, '행 선택 후 열 선택' 방식이므로 11비트로 주소 선택이 가능하다.

칩 패키징

* 향상된 DRAM 조직

전통적인 DRAM은 내부 구조와 프로세서의 기억장치 버스와의 인터페이스 문제 때문에 한계를 가지고 있다.

DRAM 성능을 해결하기 위해 DRAM과 프로세서 사이에 SRAM 캐시가 삽입되어 왔지만 효과가 크지 않았고,

수년간 기본적인 DRAM 구조에 대해 여러 보완이 이루어져 왔다.

현재 널리 사용되고 있는 DRAM 구조 방식에는 SDRAM과 DDR-DRAM이 있다.

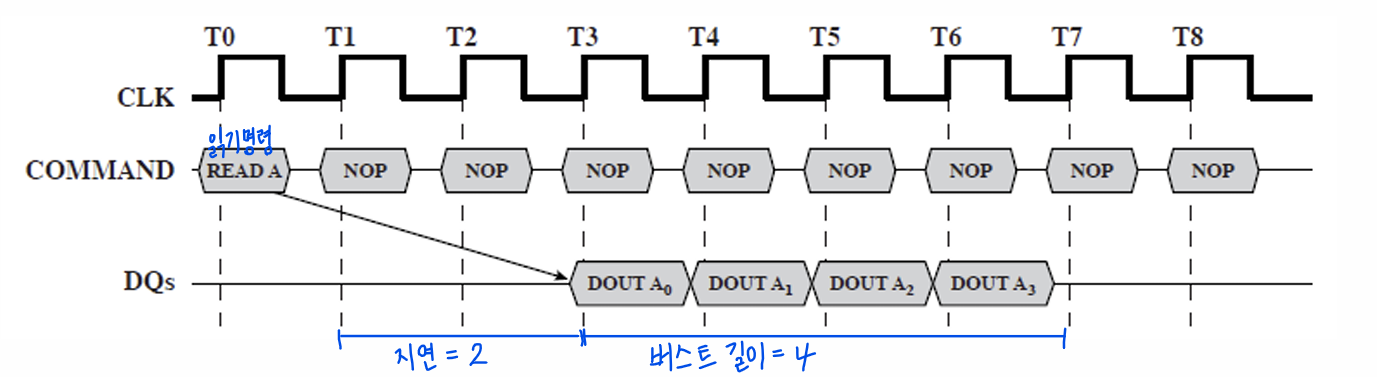

SDRAM(Synchronous DRAM: 동기식 DRAM)

SDRAM은 가장 널리 사용되고 있는 DRAM 형태이다.

기존 DRAM에서, 프로세서는 주소와 제어 신호를 기억장치로 보내어서 읽히거나 쓰여질 데이터를 지정하고, 액세스 시간만큼 지연 후 DRAM은 데이터를 읽거나 쓴다.

액세스 시간 지연 동안 DRAM은 행과 열의 커패시턴스 활성화, 데이터 감지, 데이터 출력을 위한 경로 설정 등 내부 기능들을 수행한다.

이 시간 동안 CPU는 대기만 해야 하기 때문에 시스템 성능이 저하된다.

비동기식인 전통적인 DRAM과 달리, SDRAM은 외부 클록 신호와 동기화되어 대기 상태 없이 프로세서와 데이터 교환이 가능하다.

프로세서는 명령어와 주소를 발송하고, SDRAM이 그 요구를 처리하는 동안 프로세서는 다른 업무를 수행한다.

SDRAM은 주소 준비 시간과 첫 번째 액세스 후의 행/열 선의 선충전(Precharge) 시간을 제거하기 위해 버스트 모드 (Burst Mode)를 채택하고 있다.

버스트 모드는 한 번의 액세스 동작 때 여러 바이트들을 연속적으로 전송하는 방식이다. 즉, 일련의 데이터 비트들이 첫 번째 비트가 액세스 된 후에 클록에 맞춰 출력된다.

버스트 모드는 액세스 될 모든 비트들이 순서대로 액세스 되고, 첫 번째 액세스 된 비트와 동일한 배열의 행에 있는 경우에 유용하다.

또한, SDRAM은 모든 레지스터를 사용한다.

모든 레지스터는 버스트 길이를 지정해 주는데, 여기서 길이란 버스에 동기적으로 실려지는 데이터 유니트들의 수이다.

레지스터로 버스트의 길이를 지정함으로써 읽기 요구와 데이터 전송의 시작 사이의 지연을 조정한다,

이때 큰 데이터 블록들을 연속적으로 전송할 때 가장 성능이 좋다.

DDR SDRAM(Double Data Rate DRAM)

- 데이터를 클록사이클 당 2번씩 보낼 수 있다.(상승, 하강 에지)

- 2비트 선인출 버퍼를 이용한다.(데이터 버스에 신속하게 놓이도록 미리 위치시켜 두는 것)

- 전송 속도: 200 ~ 400Mbps

DDR 2

- RAM 칩의 동작 주파수를 높인 것이다.

- 선인출 버퍼를 칩당 2비트에서 4비트로 확대하였다.

- 전송 속도: 400 ~ 1066Mbps

DDR 3

- 선인출 버퍼의 크기를 8비트로 증가하였다.

- 전송 속도: 800 ~ 2133Mbps

DDR 4

- 전송 속도: 2133 ~ 4266Mbps

성결대학교 정보통신공학과 컴퓨터구조 강의(2023)

Wiilliam Stallings, 「컴퓨터시스템구조론(10판)」

본 게시물은 위 강의 및 교재를 기반으로 정리한 글입니다.

'전공수업 > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 외부 기억장치 - 자기 디스크 (1) | 2023.12.10 |

|---|---|

| [컴퓨터 구조] 내부 기억장치 #2 - 오류 정정 (1) | 2023.11.28 |

| [컴퓨터 구조] 성능 균형, CPU 성능 향상 기법, 성능 평가 (2) | 2023.10.17 |

| [컴퓨터 구조] 버스 상호연결 (2) | 2023.10.10 |

| 컴퓨터의 핵심 부품(CPU, 메모리, I/O, 시스템 버스) (0) | 2023.10.09 |

댓글