* 참고 교재

컴퓨터 시스템 구조론 - 예스24 (yes24.com)

컴퓨터 시스템 구조론 - 예스24

컴퓨터 시스템 구조론

www.yes24.com

[한빛미디어] 혼자 공부하는 컴퓨터 구조+운영체제 (hanbit.co.kr)

[한빛미디어] 혼자 공부하는 컴퓨터 구조+운영체제

좋은 개발자는 컴퓨터를 분석의 대상으로 바라볼 뿐, 두려워하지 않는다!‘전공서가 너무 어려워서 쉽게 배우고 싶을 때’, ‘개발자가 되고 싶은데 뭐부터 봐야 하는지 모를 때’ ‘기술 면접

hongong.hanbit.co.kr

* 성능 균형(Performance Balance)

성능 균형 문제

프로세서의 속도가 증가하면서 프로세서보다 메모리의 속도가 느린 문제가 발생한다. 즉, 프로세서와 주기억장치 간 인터페이스에서 병목이 발생하는 현상을 성능 균형 문제라고 한다.

따라서 다양한 부품들의 성능 간의 불일치를 보상하기 위해 조직과 구조를 적절히 조절하는 성능 균형을 얻을 필요가 있다.

성능 균형 문제 해결 방안

1. 넓은 버스 데이터 통로를 사용하여 한 번에 가져올 수 있는 비트 수를 증가시킨다.

2. 더 빠른 속도의 버스를 사용하거나 계층적 버스 구조를 사용하여 상호연결 대역폭을 증가시킨다.

3. 프로세서 칩 내에 한 개 또는 그 이상의 캐시(Cache)를 넣어 기억 장치 액세스 빈도수를 줄인다.

I/O 성능 균형

컴퓨터들의 성능이 향상되면서 높은 I/O 요구율을 필요한 응용 프로그램 증가하고 있다.

이에 따라 입출력 장치에서도 프로세서와 주변 장치 간 데이터를 이동시키는 과정에서 성능 균형 문제가 발생한다.

이를 해결하기 위한 방안에는 캐싱(Caching)/버퍼링(Buffering), 빠른 속도의 상호 연결 버스(버스 계층화), 다중 프로세서 배치 등이 있다.

* CPU 성능 향상 기법

프로세서의 속도를 높이는 방법

프로세서와 다른 장치들과의 성능 균형을 얻는 것도 중요하지만, 프로세서의 속도를 높일 필요성도 여전히 존재한다.

1. 프로세서의 하드웨어 속도를 증가시킨다.

프로세서 칩 상의 논리 게이트들의 크기를 줄여서 게이트 밀도를 높이고 클럭 속도를 높인다.

게이트들이 더 가까이 위치하면 신호들의 전파 시간이 크게 감소하여 프로세서의 속도가 높아진다.

클럭 속도의 증가는 각 연산들이 더 빠르게 수행된다는 것을 의미한다.

2. 캐시의 크기와 속도를 증가시킨다.

프로세서 칩 자체의 한 영역을 캐시에 할애하면 캐시 액세스 시간이 감소된다.

3. 프로세서 조직과 구조를 변경한다.

명령어 파이프라인과 같은 병렬성을 이용한다.

CPU 성능 향상 시 클럭 속도와 회로 밀도 문제 발생

클럭 속도와 회로 밀도의 증가는 CPU 성능 향상에 가장 크게 기여하지만 , 아래와 같은 여러 심각한 문제들도 발생시킨다.

1. 전력(Power) 문제

칩 내부 회로의 밀도와 클럭 속도가 높아지면 전력 밀도도 증가하여 발열이 심해진다.

2. RC 지연(RC Delay)

칩 상에서 트랜지스터들 간에 흐르는 전자들의 속도는 그들을 연결해 주는 금속선들의 저항과 캐패시턴스에 의해 제한된다. 칩 상의 부품들의 크기가 작아질수록 연결선들이 더 가늘어져서 자항이 증가하며, 선들이 더 가까이 위치하면 캐패시턴스도 증가한다.

특히 RC 곱의 값이 증가함에 따라 지연도 길어진다.

3. 기억장치 지연(Memory Latency)

기억장치의 속도는 프로세서 속도보다 떨어진다. 즉, 성능균형 문제가 발생한다.

CPU 성능 향상을 위한 조직 및 구조적 방법

따라서 성능 향상을 위해 클럭 속도와 회로 밀도의 증가보다는 조직 및 구조적 방법을 사용하는 것이 더 강조되고 있다.

1. 캐시 용량 증가

프로세서와 주기억장치 사이에 두 레벨 또는 세 레벨의 캐시들을 설치한다. 칩 밀도가 높아질수록 더 많은 캐시 기억장치가 칩 내부에 들어가게 됨으로써 캐시 액세스가 더 빨라진다.

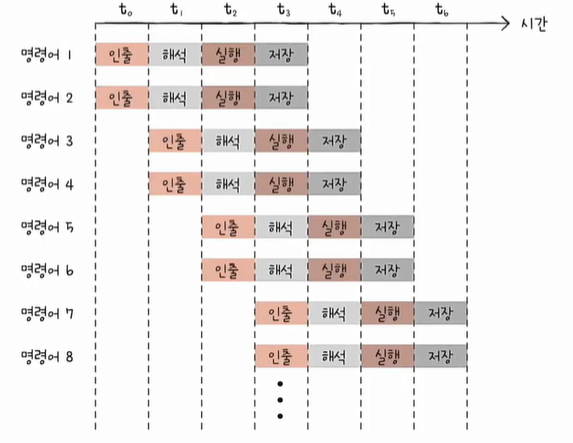

2. 명령어 병렬 처리 기법 - 파이프라이닝(Pipelining)

명령어는 명령어 인출(Instruction Fetch), 명령어 해석(Instruction Decode), 명령어 실행(Execute Instruction), 결과 저장(Write Back) 단계로 처리된다. 이때 같은 단계가 겹치지만 않으면 CPU는 각 단계를 동시에 실행할 수 있다.

파이프라이닝은 파이프라인을 따라 여러 단계들에서 서로 다른 명령어들이 동시에 실행되게 해 준다.

3. 명령어 병렬 처리 기법 2 - 슈퍼스칼라(Superscalar)

슈퍼스칼라는 하나의 CPU 내부에 여러 개의 파이프라인들을 두어서 서로 의존관계가 없는 명령어들이 병렬로 실행되게 해 준다.

4. 멀티코어(Multicore)

코어(Core)란 CPU 내에서 명령어를 실행하는 부품으로, 2개 이상의 코어를 포함하고 있는 CPU를 멀티코어라고 한다.

다시 말해, 멀티코어는 대용량 캐시를 공유하는 여러 프로세서들을 같은 칩에 넣는 방법이다.

즉, 하나의 복잡한 프로세서를 사용하기보다는 칩 상에서 더 간단한 두 개의 프로세서들을 사용하는 것이다.

프로세서 내부에서 성능 향상은 복잡도 증가의 제곱근에 비례한다. 만약 소프트웨어가 다중 프로세서를 이용한다면 프로세서 수를 두 배로 늘리면 성능도 두 배가 된다.

기억장치 회로의 소비전력이 프로세서 회로보다 훨씬 적기 때문에 두 개의 프로세서와 함께 대용량 캐시를 두는 것도 좋다.

* 성능 평가

클럭 속도

클럭 속도는 헤르츠(Hz) 단위로 측정된다. 헤르츠는 1초에 클럭이 반복되는 횟수를 의미한다.

예를 들어 클럭이 '똑-딱-' 하고 1초에 1번 반복되면 1Hz이고, 클릭이 1초에 100번 반복되면 100Hz이다.

프로세서의 속도는 클럭에 의해 발생되는 펄스 주파수(초당 사이클 수, Hz)에 의해 결정된다.

펄스들 간의 시간은 사이클 시간(클럭률)과 같고, 명령어 실행을 위해 여러 클럭 사이클이 소요된다.

명령어 실행률(MIPS)

명령어 세트의 차이

CISC(Complex Instruction Set Computer)는 복잡한 명령어 집합을 활용하는 컴퓨터로, 명령어의 형태와 크기가 다양한 가변 길이 명령어를 활용한다.

RISC(Reduced Instruction Set Computer)는 CISC와 달리 명령어 종류가 적고 짧고 규격화된 고정 길이 명령어를 활용하는 컴퓨터이다.

RISC는 명령어 종류가 적어서 'A = B + C' 명령을 실행하기 위해서는 명령어가 4개나 쓰인다.

암달의 법칙

단일 프로세서와 비교하여 다수의 프로세서들을 사용한 프로그램 속도 향상 정도를 다룬다.

N개의 프로세서를 가진 병렬 프로세서를 사용하여 그 프로그램의 병렬 부분을 완전히 이용하는 경우에 얻을 수 있는 속도 향상은 아래와 같이 계산한다.

성결대학교 정보통신공학과 컴퓨터구조 강의(2023)

Wiilliam Stallings, 「컴퓨터시스템구조론(10판)」

강민철, 「혼자 공부하는 컴퓨터구조+운영체제」

본 게시물은 위 강의 및 교재를 기반으로 정리한 글입니다.

'전공수업 > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 외부 기억장치 - 자기 디스크 (1) | 2023.12.10 |

|---|---|

| [컴퓨터 구조] 내부 기억장치 #2 - 오류 정정 (1) | 2023.11.28 |

| [컴퓨터 구조] 내부 기억장치 - 반도체 주기억장치, 향상된 DRAM 조직 (1) | 2023.11.27 |

| [컴퓨터 구조] 버스 상호연결 (2) | 2023.10.10 |

| 컴퓨터의 핵심 부품(CPU, 메모리, I/O, 시스템 버스) (0) | 2023.10.09 |

댓글